#2

Atty. Docket No. <u>678-724</u> (P9876)

### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

APPLICANT(S):

Takahiko KISHI

SERIAL NO.:

09/931,124

AND RECEIVER

GROUP: Art Unit - Not yet assigned

FILED:

August 16, 2001

DATED:

September 13, 2001

FOR:

DIGITAL DOWN-CONVERTER

RECEIVED

OCT 1 6 2001

**Technology Center 2600**

**Assistant Commissioner for Patents** Washington, D.C. 20231

### TRANSMITTAL OF PRIORITY DOCUMENT

Sir:

Attached is a certified copy of Japanese Appln. No. 247862/2000 filed on

August 17, 2000 from which priority is claimed under 35 U.S.C. §119.

Respectfully submitted,

Paul J. Farrell

Reg. No. 33,494

Attorney for Applicant(s)

fauel

DILWORTH & BARRESE, LLP 333 Earle Ovington Blvd. Uniondale, NY 11553 (516) 228-8484

### CERTIFICATE OF MAILING UNDER 37 C.F.R. §1.8(a)

I hereby certify that this correspondence is being deposited with the United States Postal Service as first class mail, postpaid in an envelope addressed to the: Assistant Commissioner for Patents, Washington, D.C. 20231 on September 13, 2001.

Dated: September 13, 2001

# 日本国特許庁 JAPAN PATENT OFFICE

RECEIVED

OCT 1 6 2001

Technology Center 2600

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office

出願年月日 Date of Application:

2000年 8月17日

出願番号 Application Number:

特願2000-247862

出 願 人 Applicant(s):

株式会社サムスン横浜研究所

CERTIFIED COPY OF PRIORITY DOCUMENT

2001年 8月 3日

特許庁長官 Commissioner, Japan Patent Office

書類名 TRADEMAN

特許願

【整理番号】

00062104

【提出日】

平成12年 8月17日

【あて先】

特許庁長官 殿

【国際特許分類】

H04B 10/06

【発明の名称】

デジタルダウンコンバータ、及び受信機

【請求項の数】

5

【発明者】

【住所又は居所】

神奈川県横浜市鶴見区菅沢町2-7 株式会社サムスン

横浜研究所 電子研究所内

【氏名】

岸 孝彦

【特許出願人】

【識別番号】

598045058

【氏名又は名称】

株式会社サムスン横浜研究所

【代理人】

【識別番号】

100064908

【弁理士】

【氏名又は名称】

志賀 正武

【選任した代理人】

【識別番号】

100108578

【弁理士】

【氏名又は名称】

髙橋 詔男

【選任した代理人】

【識別番号】

100089037

【弁理士】

【氏名又は名称】

渡邊 隆

【選任した代理人】

【識別番号】

100101465

【弁理士】

【氏名又は名称】 青山 正和

【選任した代理人】

【識別番号】 100094400

【弁理士】

【氏名又は名称】 鈴木 三義

【選任した代理人】

【識別番号】 100107836

【弁理士】

【氏名又は名称】 西 和哉

【選任した代理人】

【識別番号】 100108453

【弁理士】

【氏名又は名称】 村山 靖彦

【手数料の表示】

【予納台帳番号】 008707

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【包括委任状番号】 9812566

【プルーフの要否】

【書類名】

明細書

【発明の名称】

デジタルダウンコンバータ、及び受信機

【特許請求の範囲】

【請求項1】 無線受信手段で受信され、無線周波数または中間周波数でサンプリングされた受信信号の周波数を検波処理するための検波用周波数に変換するデジタルダウンコンバータにおいて、

前記受信信号の周波数を第1のIF周波数に変換する第1のミキサー手段と、

前記第1のミキサー手段によって変換された前記第1のIF周波数の信号を前記検波用周波数である第2のIF周波数の信号に変換し、さらに、複素化する第2のミキサー手段と、

を具備することを特徴とするデジタルダウンコンバータ。

【請求項2】 前記第1のIF周波数は、前記サンプリングの周波数の1/4倍であることを特徴とする請求項1に記載のデジタルダウンコンバータ。

【請求項3】 前記デジタルダウンコンバータは、前記第1のミキサー手段の出力を増幅する自動利得増幅器を具備することを特徴とする請求項1または請求項2に記載のデジタルダウンコンバータ。

【請求項4】 前記第2のミキサー手段は、デシメーションフィルタと直交変換器とを備えたポリフェーズ構成を用いることを特徴とする請求項2に記載のデジタルダウンコンバータ。

【請求項5】 請求項1乃至請求項4のいずれかの項に記載のデジタルダウンコンバータを備え、

前記デジタルダウンコンバータで周波数変換される受信信号を受信するための 無線受信手段と、

前記無線受信手段の出力からエイリアシング周波数成分と、前記デジタルダウンコンバータに具備された第1のミキサー手段のイメージ周波数成分とを減衰させるフィルタと、

前記フィルタの出力を無線周波数または中間周波数でサンプリングして、前記 デジタルダウンコンバータに入力するアナログ・デジタル変換器と、

を具備することを特徴とする受信機。

### 【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、無線受信信号をRF(無線周波数)またはIF(中間周波数)でサンプリングしてデジタル信号処理するデジタルダウンコンバータ、及び受信機に関する。

[0002]

【従来の技術】

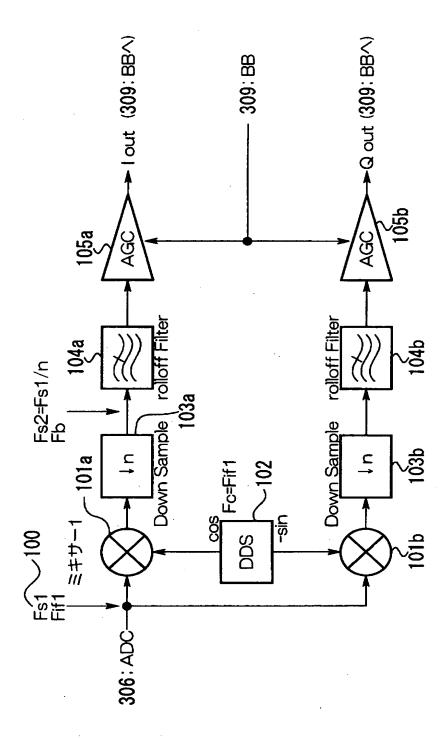

従来のデータ通信受信機におけるデジタル信号処理回路の周波数変換部の1例 、すなわち、デジタルダウンコンバータ(DDC)を図4を参照して説明する。 このDDCに入力する信号100はRF帯あるいはIF帯の変調波であって、 周波数Fs1のサンプル信号、およびこのサンプル信号により変調されている周波 数Fif1の中間周波キャリアである。このDDC入力信号は、ミキサー101aお よびミキサー101bにおいて、ローカル発振器(DDS)102から出力され る周波数Fcのcos波とsin波と混合、検波される。このDDS102から出力され るcos波とsin波の周波数FcがFc=Fif1の関係を満たすように設定されていると、 前記入力波は一気にサンプル信号のみに関する検波処理周波数に変換される。さ らに、この検波されたサンプル信号はサンプリングレート変換器103a,およ び103bにより1/nにダウンサンプルされ(Fs2=Fs1/n)、周波数Fbのベースバン ド信号が再生される。このベースバンド信号の波形はロールオフ・フィルタ10 4 a,および104 bによりロールオフ整形され、さらに自動利得増幅器(AG C) 105aおよび105bにおいて可変増幅されて出力される。サンプル信号 は二つのベースバンド信号、すなわち同相成分 I 信号と直交成分Q信号として出 力されている。

[0003]

上述のごとく、RF又はIFにて受信信号をサンプリングし、デジタル信号処理によって信号の選択及び検波を行う受信機において、サンプリングした信号を処理する信号処理回路としてのデジタルダウンコンバータ(DDC)においては、Real-Complexミキサー(直交変換回路)によって一気に検波処理

周波数(一般的にベースバンド)に変換する方法が一般的であった。

このとき、IF信号をサンプリングするためには高速なサンプリング周波数が要求される。さらに、ダウンサンプル処理によってサンプリング周波数を下げて消費電力を低減できる後段部より、ミキサー部とローカル発振部の消費電力は動作速度が速いために大きい。

cos波とsin波を出力するDDSは、周波数演算部とROM(リードオンリメモリ)を一つとしても、一サンプリング周期にcosとsinのデータを読み出すために2度データを読み出す。このため、消費電力の多くを占めるROMの消費電力は2度のアドレスと出力データの変化により2回路と同等になり、DDSとしての消費電力も単一波出力の2倍近い電力を消費する。

また、IF周波数を周波数オフセットの無いベースバンドに変換するために高精度が必要で(細かい周波数ステップ)、スプリアスも少ない信号を得るためには位相演算回路の演算語長を長く取り、ROMのサイズも大きくする必要がある

[0004]

#### 【発明が解決しようとする課題】

しかしながら従来のDDCにおいては、次のような課題がある。第1に、IF 信号をサンプリングするためには高速なサンプリング周波数が要求される。さらに、初段のミキサーとミキサーにローカルを供給するローカル発振器(DDS)はサンプリング周波数と同じ周波数で動作するために高速で動作し、その消費電力は、DDC消費電力の大きなウェイトを占める。ダウンサンプル処理によってサンプリング周波数を下げた後段部の消費電力と比較して、前者の消費電力は大きい。

cos波とsin波を出力するDDS102は、周波数演算部とROMを一つとしても、一サンプリング周期にcosとsinのデータを読み出すために2度データを読み出す。このため、消費電力の多くを占めるROMの消費電力は2度のアドレスと出力データの変化により2回路と同等になり、DDSとしての消費電力も単一波出力の2倍近い電力を消費する。

[0005]

また、IF周波数を周波数オフセットのないベースバンドに変換するために高精度が必要で(細かい周波数ステップ)、スプリアスも少ない信号を得るためには位相演算回路の演算語長を長く取り、ROMのサイズも大きくする必要がある

上述のごとく従来のDDCにおいては、初段のミキサー101a,101bとミキサーにローカルを供給するローカル発振器(DDS)102は、AD変換のサンプリング周波数と同じ周波数で動作するために高速で動作する。このため初段のミキサー101a,101bとミキサーにローカルを供給するローカル発振器(DDS)102における消費電力は、DDC消費電力の大きなウェイトを占める。

#### [0006]

本発明は、このような事情を考慮してなされたもので、その目的は、消費電力 を低減することができるデジタルダウンコンバータ、及び受信機を実現すること にある。

#### [0007]

#### 【課題を解決するための手段】

上記の課題を解決するために、請求項1に記載の発明は、無線受信手段で受信され、無線周波数または中間周波数でサンプリングされた受信信号の周波数を検波処理するための検波用周波数に変換するデジタルダウンコンバータにおいて、前記受信信号の周波数を第1のIF周波数に変換する第1のミキサー手段と、前記第1のミキサー手段によって変換された前記第1のIF周波数の信号を前記検波用周波数である第2のIF周波数の信号に変換し、さらに、複素化する第2のミキサー手段とを具備することを特徴とする。

#### [0008]

請求項2に記載の発明は、請求項1に記載の発明において、前記第1のIF周 波数は、前記サンプリングの周波数の1/4倍であることを特徴とする。

請求項3に記載の発明は、請求項1または請求項2に記載の発明において、前 記デジタルダウンコンバータは、前記第1のミキサー手段の出力を増幅する自動 利得増幅器を具備することを特徴とする。

請求項4に記載の発明は、請求項2に記載の発明において、前記第2のミキサー手段は、デシメーションフィルタと直交変換器とを備えたポリフェーズ構成を用いることを特徴とする。

### [0009]

請求項5に記載の受信機の発明は、請求項1乃至請求項4のいずれかの項に記載のデジタルダウンコンバータを備え、前記デジタルダウンコンバータで周波数変換される受信信号を受信するための無線受信手段と、前記無線受信手段の出力からエイリアシング周波数成分と、前記デジタルダウンコンバータに具備された第1のミキサー手段のイメージ周波数成分とを減衰させるフィルタと、前記フィルタの出力を無線周波数または中間周波数でサンプリングして、前記デジタルダウンコンバータに入力するアナログ・デジタル変換器とを具備することを特徴とする。

### [0010]

### 【発明の実施の形態】

本発明の実施形態によるデジタルダウンコンバータ(DDC)は、入力した I F信号またはRF信号を、DDC内初段のRealミキサーによりDDC内第1 の I F周波数の信号に変換し、該第1のIF周波数の信号をRealーComplexミキサー(直交変換器)によってDDC内第2のIF周波数、すなわち検波処理するための検波用周波数の信号に変換すると共に複素化するデジタル処理 回路として構成されるものである。

#### [0011]

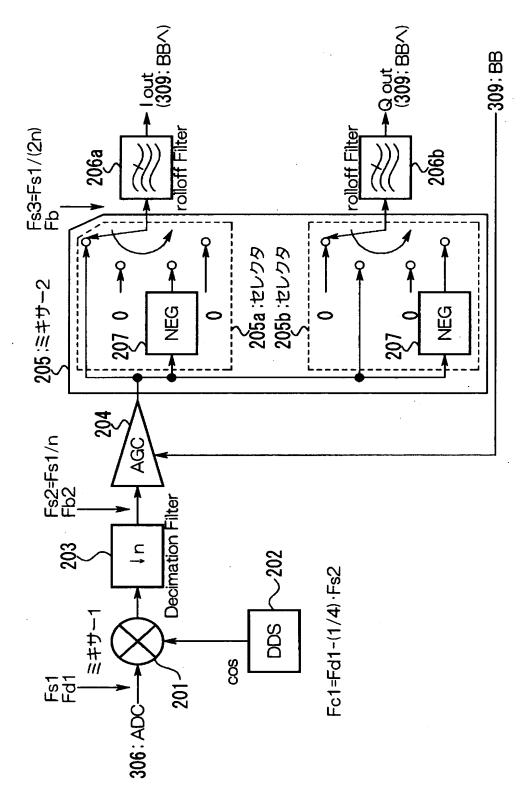

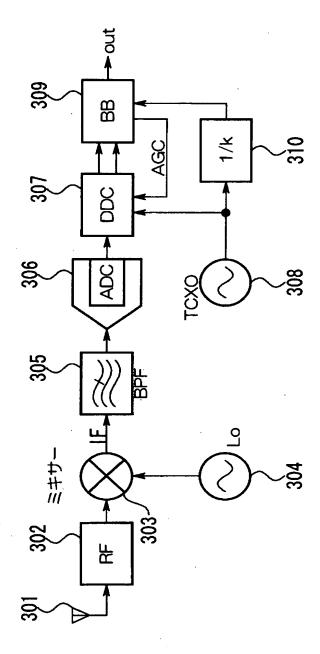

以下、図面を参照し本発明の実施形態について説明する。図1は本発明の第1の実施形態によるデジタルダウンコンバータ(DDC)307の構成を示すブロック図である。図2は同実施形態のDDC307を構成要素とする受信機の構成を示すブロック図である。

図2において、アンテナ301により受信された受信信号は、RF部302、ミキサー303、ローカル発信器(Lo)304においてIF信号に変換され、このIF信号は、帯域通過形フィルタ(BPF)のIFフィルタ305により受信バンド以外の信号を抑圧すべく帯域制限される。アナログ/デジタル(AD)

変換器306は、IFフィルタ305の出力を入力し、サンプリング後、受信信号周波数Fd1のデジタル信号に変換されたデジタルIF信号をDDC307に入力する。AD変換器306のサンプリング周波数はFs1である。このデジタルIF信号は、(1)式で表される。

デジタル I F信号=f1(t)·cos(nωd1 t)···(1)

なお、符号308はローカル発振器 (TCXO)、符号309はベースバンド回路 (BB)、符号310はBB回路で用いるクロックを生成する分周回路 (1/k) である。

[0012]

図1において、Realミキサーである第1の乗算器(ミキサー)201は、上記(1)式で表されたデジタルIF信号とローカル発振器(DDS)202から出力された周波数Fc1のローカル信号c(t)(但し、 $c(t)=cos(n\omega c1t)$ で表される)とを入力し、これら入力した信号を乗算する。この乗算の結果、デジタルIF信号の周波数は、周波数Fs1の1/32の周波数Fd2に変換される。この周波数変換されたデジタルIF信号f2(t)は、(2)式で表される。この時の周波数の関係は、(3)式で表される。

f 2 (t) = f1(t)

$$\cos(n (\omega d 1 \pm \omega c 1) t) \cdot \cdot \cdot (2)$$

F c.1 = F d 1 - F s 1/3 2  $\cdot \cdot \cdot (3)$

次いで、デシメーションフィルタ 2 0 3 は、第 1 のミキサー 2 0 1 の出力 f 2 (t)を入力し、周波数 (Fd1+Fc1)の信号を抑圧するとともに、周波数Fs1の 1 / 8のサンプリング周波数Fs2にダウンサンプルする。この周波数Fs2にダウンサンプルされたデジタル I F信号 f 2 (t) は、上記 (2)式の n=8 m であり、 (4)式で表される。この時の周波数の関係は、F s 1=8 × F s 2 より、 (5)式で表される。

f 2 (t) =

$$(1/2)$$

f 1 (t)  $e^{jm(\omega d_1 - \omega c_1)t}$  · · · (4)

F c 1 = F d 1 -  $(1/4)$  × F s 2 · · · (5)

[0014]

次いで、上記(4)式で表されたデジタルIF信号 f 2(t)は、自動利得増幅器(AGC)204において増幅された後、第2のミキサー205に入力される。この第2のミキサー205は、入力したデジタルIF信号 f 2(t)をサンプリング周波数の1/4 すなわちfc2=(1/4)×fs2と乗算して、検波処理するための検波用周波数(第2のIF周波数)のベースバンド信号 f b(t)に変換する。この変換は、(6)式で表される。

f b (t) = (1/2) f 1 (t) e

$$jm(\omega d1 - \omega c1 - \omega c2)t$$

= (1/2) f 1 (t) e  $jm\{\omega d1 - \{(\omega s2)/4\}\} - \{(\omega s2)/4\}\}$

$$= (1/2) f 1 (t) \cdots (6)$$

[0015]

次いで、このベースバンド信号fb(t)は、ロールオフフィルタ206a、および206bによりロールオフ整形され、同相成分Iおよび直交成分Qの複素化信号が出力される。

[0016]

なお、上記第2のミキサー205は、Real-Complexミキサー(直交変換器)であって、AGC204の出力にサンプリング周波数の1/4を乗算する乗算器とこの乗算された信号を複素化する複素化手段とから構成されることになるが、その乗算値は、ミキサー用ローカル発振のcosとして1,0,-1,0,1 $\cdots$ 、sinとして0,1,0,-1,0, $\cdots$ となる。これより、第2のミキサー205は、図1に示すように、セレクタ205a及び205bによって、簡易に構成することが可能である。

セレクタ205 a は、ローカル発振のcosとして1, 0, -1, 0, 1, …、のように、乗算値を巡回して選択するセレクタであって、4つの入力から一つを選択して出力する。この4つの入力とは、乗算値「1」に対応した乗算結果であるAGC204の出力と、乗算値「0」に対応した乗算結果の「0」と、乗算値「-1」に対応した乗算結果であって、AGC204の出力を符号反転する符号反転回路207の出力と、乗算値「0」に対応した乗算結果の「0」とである。

### [0017]

また、セレクタ205bは、ローカル発振のsinとして 0, 1, 0, -1, 0, …、のように、乗算値を巡回して選択するセレクタであって、上記セレクタ205aと同様に、4つの入力から一つを選択して出力する。この4つの入力とは、乗算値「0」に対応した乗算結果の「0」と、乗算値「1」に対応した乗算結果であるAGC204の出力と、乗算値「0」に対応した乗算結果の「0」と、乗算値「-1」に対応した乗算結果であって、AGC204の出力を符号反転する符号反転回路207の出力とである。

### [0018]

上記実施形態においては、従来のように入力信号を一度に目的周波数に変換するのではなく、精度を必要とするチューニングのための変換と複素化のための変換とを分けることによって、回路規模と消費電力の低減が可能である。

#### [0019]

なお、上記DDC入力周波数において、fd1'=fc1-(fs1/32) は第1のミキサー201のイメージ周波数となるが、AD変換器306の上流の アナログフィルタ(IFフィルタ305)で妨害信号を抑圧する。チャネル帯域 への制限は、DDC307内にて行えるので、このアナログフィルタの役割は、 エイリアシング周波数とイメージ周波数の妨害信号の抑圧のみで良い。

また、上記実施形態においては、DDC307内の第1のIF周波数をサンプリング周波数の1/4倍とすることによって、第2のIF周波数に係る処理(第2のミキサー205の処理)の簡略化が可能である。

#### [0020]

なお、上記実施形態において、第2のミキサー205の処理は、サンプリング 周波数が低減されたあとの処理である上に、そのミキサー処理が簡略化されるの で、第2のミキサー205で発生する消費電力は、DDC307で発生する総消 費電力に比して僅かである。

#### [0021]

ところで、デジタル受信機における一般的構成は、従来例における説明のよう にベースバンドに一気に変換する。この方式は、ベースバンド変換後のデシメー ションフィルタ、ロールオフフィルタが全てLPFで構成できるというメリットがある(BPFの方がLPFよりフィルタ次数が高くなる)。従来例ではこのようなメリットがあるために、上記実施形態のように中間IFをデジタル信号処理部内に設けることは顧みられ無かった。一方、従来例ではベースバンドにあるAGC105aおいて、自動利得によるAGC105aのゲイン可変時に発生する受信信号歪の多くが受信信号帯域内に落ちる。このため、AGC105aによって発生する歪をフィルタによって低減することができないために、AGC処理自体の歪を低減するAGC低歪化のために処理アルゴリズムの工夫が必須であった

#### [0022]

そこで、上記実施形態においては、AGC204をデジタルIF信号処理部内の第2のミキサー205の上流に設置することにより、AGC204で発生するハーモニック歪は受信信号帯域外に落ちるようになる。受信信号帯域外の歪を、目的外信号とエイリアシング信号を抑圧するIFフィルタ305で抑圧することで、AGC処理の工夫をすることなく、従来のAGC処理によって発生する歪を低減することができる。

#### [0023]

また、上記DDS202は、周波数Fc1の位相演算部とこの位相演算部の出力に対応した振幅値が書き込まれたROMとから構成されており、このROMの出力を周波数Fc1のローカル信号c(t)として出力する。

このDDS202において、位相誤差を原因とするスプリアス特性は、位相演算部とROMの位相語長(アドレス長、すなわちROM容量)の差(再量子化誤差)を1bit減じる毎に6.02dB改善される。また、ROMデータ長を1bit長くする毎に、DDS202の出力語長(ROMデータ長)を原因とするスプリアス特性は、6.02dB改善される。このスプリアス特性改善の為に、例えば位相演算語長を固定とすると、ROMのアドレス語長を1bit増す毎に回路規模サイズ(ROM容量)が2倍となり、消費電力もほぼ2倍となってしまう。

しかしながら、消費電力の制限がそれほど厳しくない受信機においては、上記 実施形態により低減した回路と消費電力をROM容量(アドレス長、データ長) の増加に利用し、ローカル発振部 (DDS) 202のスプリアス特性を改善することが可能である。

### [0024]

上述したように、本発明の実施形態によれば、初段のミキサーが2個から1個へ半減し、ローカル発振回路もcos波またはsin波の一波のみの出力で済む。初段ミキサー信号とサンプリング周波数を下げるデシメーションフィルタ回路も半減するので、本発明のデジタルダウンコンバータにおいては、従来、最も高速な処理が要求された初段ミキサー、ローカル発振およびデシメーションフィルタにおける消費電力をほぼ半減させることができる。

#### [0025]

さらに、第2のミキサー205は、入力周波数をサンプリング周波数の1/4倍とすることによりスルーと反転とセレクタで実現でき、乗算器を用いる必要が無い。このために第2のミキサー205を実現する回路が大きく簡略化される。この結果、消費電力のウェイトが高く、高速に動作する従来のミキサー回路が大きく簡略化されて、DDCの消費電力のさらなる低減が可能である。

#### [0026]

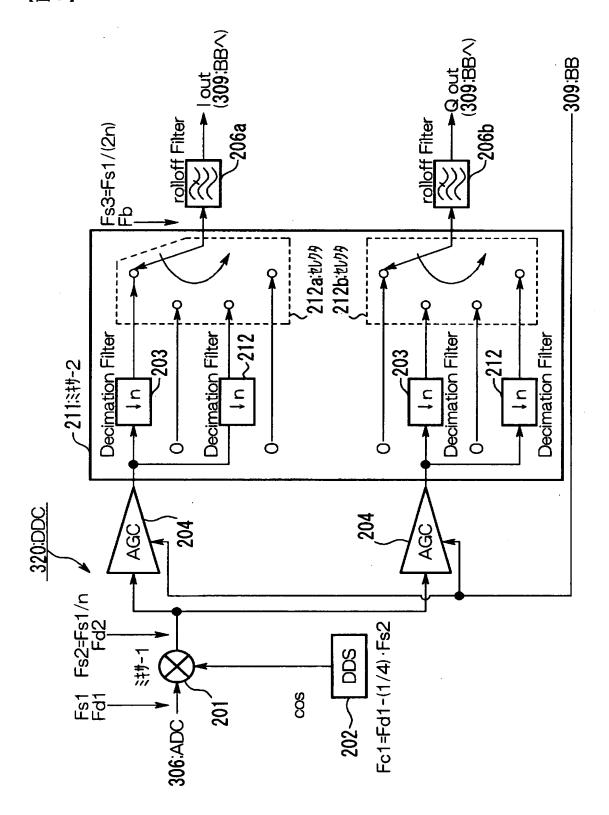

図3は本発明の第2の実施形態によるデジタルダウンコンバータ(DDC)320の構成を示すブロック図である。同図において図1の各部に対応する部分には同一の符号を付け、その説明を省略する。図3に示すDDC320は、図1に示すDDC307のデシメーションフィルタ203と第2のミキサー(直交変換器)205とを組み合わせたポリフェーズ構成を用いたものである。実際にデジタルダウンコンバータ(DDC)を構成する場合には、このポリフェーズ構成が一般的によく用いられる。

図3のDDC320において、第2のミキサー211は、図1の第2のミキサー205と同様に、ローカル発振のcos部分とsin部分とから構成される。ローカル発振のcos部分は、セレクタ212aと2個のデシメーションフィルタ203、212とから構成され、また、ローカル発振のsin部分は、セレクタ212bと2個のデシメーションフィルタ203、212とから構成される。なお、デシメーションフィルタ212は、係数の符号が反転されており、符号反転機能も有

している。また、AGC204を2個設け、それぞれ第1のミキサー201の出力を増幅し、ローカル発振のcos部分とsin部分とに入力する。

[0027]

上記第2のミキサー211のcos部分及びsin部分においては、それぞれ乗算値「1」に対応した乗算結果として、第1のミキサー201の出力をAGC204で増幅し、デシメーションフィルタ203を介してセレクタ212a及び212bに入力する。また、乗算値「-1」に対応した乗算結果として、第1のミキサー201の出力をAGC204で増幅し、デシメーションフィルタ212を介してセレクタ212a及び212bに入力する。

なお、第2のミキサー211においては、第1のミキサー201からの入力周波数Fs2 (第1のIF周波数) がサンプリング周波数Fs1の1/n倍であり、第2のミキサー211の動作周波数は、Fs2=Fs1/nとなる。ここで、第2のミキサー211はサンプリング位相毎に、動作するパス(セレクタ212a、212bが選択する入力)を切り替えるので、第2のミキサー211でのサンプリング周波数がFs2であるにもかかわらず、第2のミキサー211の各パスの動作は、周波数Fs2の1/4倍となる。この時の周波数の関係は、(7)式で表される。

(1/4) Fs2=(1/2) Fs3=(1/4n) Fs1・・・(7) さらに、第2のミキサー211においては、出力が「0」になるサンプルを間引きしているので、エイリアシング未発生の状態でダウンサンプリングすることが可能である。この時の周波数の関係は、(8) 式で表される。

$F s 3 = F s 2 / 2 = F s 1 / (2 n) \cdot \cdot \cdot (8)$

[0028]

ところで、このポリフェーズ構成で第2のミキサー211を構成する場合、通常、乗算器をcos部分及びsin部分に各1個ずつ都合2個を使用することになる。しかしながら、上述した第2の実施形態によるDDC320において、第1の実施形態と同様に、第2のミキサー211への入力周波数をサンプリング周波数Fs1の1/4倍とすることにより、乗算器を用いずに実現することができる。このため、ポリフェーズ構成でデジタルダウンコンバータ(DDC)を構成する場合でも、上述したように、第1のIF周波数をサンプリング周波数の1/4倍とす

ることによって、第2のミキサー211の回路が大きく簡略化され、DDCの消費電力の低減が可能である。

なお、上述した第2の実施形態によるDDC320を図2に示す受信機の構成要素として、第1の実施形態によるDDC307の代わりに用いるようにしてもよい。

#### [0029]

また、上述した実施形態によるDDC307は、携帯端末、あるいは、携帯電話機やその基地局装置、放送装置などに具備された受信機に適用可能であり、上記DDCの消費電力低減によって以下に示すような効果が得られる。

- ①. 携帯端末や携帯電話機等の端末においては、その連続使用時間をより長くすることができる。また、従来と同一の連続使用時間であれば、使用するバッテリ 容量が小さくてすみ、バッテリの小型化が可能である。

- ②. 基地局装置や放送装置等においては、受信機の発熱量が減るので、その放熱構造の簡易が可能となり、その結果、装置の小型化を行うことができる。

- ③. 上記DDC307においては、そのデジタル信号処理演算が簡略化される。 この結果、DDC307を用いた受信機で、消費電力削減よりもその性能改善が 課題である場合には、従来に比して、高度なアルゴリズム処理の演算量やデジタ ル信号処理演算語長を、その簡略化された演算量に相当する分、すなわち、低減 されるべき消費電力の代わりにその消費電力低減相当分増やすことができる。

#### [0030]

以上、本発明の実施形態を図面を参照して詳述してきたが、具体的な構成はこの実施形態に限られるものではなく、本発明の要旨を逸脱しない範囲の設計等も含まれる。

### [0031]

#### 【発明の効果】

以上説明したように、本発明によれば、無線受信手段で受信され、無線周波数 または中間周波数でサンプリングされた受信信号の周波数を検波処理するための 検波用周波数に変換するデジタルダウンコンバータにおいて、受信信号の周波数 を第1のIF周波数に変換する第1のミキサー手段と、第1のミキサー手段によ って変換された第1のIF周波数の信号を検波用周波数である第2のIF周波数 の信号に変換し、さらに、複素化する第2のミキサー手段とを具備するようにしたので、従来、最も高速な処理が要求された初段ミキサー、ローカル発振および デシメーションフィルタの構成が簡略化され、この結果、消費電力を低減することができる。

[0032]

さらに、第1のIF周波数をサンプリングの周波数の1/4倍とすれば、消費電力のウェイトが高く、高速に動作する従来のミキサー回路が大きく簡略化されるので、消費電力のさらなる低減が可能である。

### 【図面の簡単な説明】

- 【図1】 本発明の第1の実施形態によるデジタルダウンコンバータ (DDC) 307の構成を示すブロック図である。

- 【図2】 図1に示すDDC307を構成要素とする受信機の構成を示すブロック図である。

- 【図3】 本発明の第2の実施形態によるデジタルダウンコンバータ(DDC)320の構成を示すブロック図である。

- 【図4】従来のデジタルダウンコンバータの構成を示すブロック図である。

#### 【符号の説明】

- 201 第1のミキサー(ミキサー1)

- 202 ローカル発振器

- 203、212 デシメーションフィルタ

- 204 AGC(自動利得增幅器)

- 205、211 第2のミキサー(ミキサー2)

- 205a, 205b, 212a, 212b セレクタ

- 206a、206b ロールオフフィルタ

- 207 符号反転回路

- 301 アンテナ

- 302 RF部

- 303 ミキサー

- 304 ローカル発振器

- 305 フィルタ (BPF)

- 306 AD変換器

- 307、320 デジタルダウンコンバータ (DDC)

- 308 ローカル発振器 (TCXO)

- 309 ベースバンド回路

- 310 分周回路

【書類名】

図面

【図1】

【図2】

【図3】

【図4】

【書類名】

要約書

【要約】

【課題】 消費電力を低減することができるデジタルダウンコンバータ、及び受信機を実現することにある。

【解決手段】 無線受信手段で受信され、無線周波数または中間周波数でサンプリングされた受信信号の周波数を検波処理するための検波用周波数に変換するデジタルダウンコンバータにおいて、第1のミキサー201は、受信信号の周波数を第1のIF周波数に変換する。第2のミキサー205は、第1のミキサー201によって変換された第1のIF周波数の信号を検波用周波数である第2のIF周波数の信号に変換し、さらに、複素化する。

【選択図】 図1

## 認定・付加情報

特許出願の番号 特願2000-247862

受付番号 50001046854

書類名特許願

担当官 第七担当上席 0096

作成日 平成12年 8月18日

<認定情報・付加情報>

【特許出願人】

【識別番号】 598045058

【住所又は居所】 神奈川県横浜市鶴見区菅沢町2-7

【氏名又は名称】 株式会社サムスン横浜研究所

【代理人】 申請人

【識別番号】 100064908

【住所又は居所】 東京都新宿区高田馬場3丁目23番3号 ORビ

ル 志賀国際特許事務所

【氏名又は名称】 志賀 正武

【選任した代理人】

【識別番号】 100108578

【住所又は居所】 東京都新宿区高田馬場3丁目23番3号 ORビ

ル 志賀国際特許事務所

【氏名又は名称】 高橋 韶男

【選任した代理人】

【識別番号】 100089037

【住所又は居所】 東京都新宿区高田馬場3丁目23番3号 ORビ

ル 志賀国際特許事務所

【氏名又は名称】 渡邊 隆

【選任した代理人】

【識別番号】 100101465

【住所又は居所】 東京都新宿区高田馬場3丁目23番3号 ORビ

ル 志賀国際特許事務所

【氏名又は名称】 青山 正和

【選任した代理人】

【識別番号】 100094400

【住所又は居所】 東京都新宿区高田馬場3丁目23番3号 ORビ

ル 志賀国際特許事務所

次頁有

# 認定・付加情報(続き)

【氏名又は名称】

鈴木 三義

【選任した代理人】

【識別番号】

100107836

【住所又は居所】

東京都新宿区高田馬場3丁目23番3号 ORビ

ル 志賀国際特許事務所

【氏名又は名称】

西 和哉

【選任した代理人】

【識別番号】

100108453

【住所又は居所】

東京都新宿区高田馬場3丁目23番3号 ORビ

ル 志賀国際特許事務所

【氏名又は名称】

村山 靖彦

### 出願人履歴情報

識別番号

[598045058]

1. 変更年月日 1998年 3月20日

[変更理由] 新規登録

住 所 神奈川県横浜市鶴見区菅沢町2-7

氏 名 株式会社サムスン横浜研究所